信息技术在当今社会发挥着越来越重要的作用,而CPU作为其中核心技术之一,它的结构原理是计算机领域从业人员必备的专业知识。本实验吸收了计算机体系结构领域最新发展成果,以行业最新且极具发展潜力的RISC-V作为CPU设计的目标;在课程前期完成的逻辑电路实验的基础上,进一步设计CPU数据通路及控制器,并利用远程FPGA虚拟实验平台进行验证调试。

通过学习和训练,学习者能够从设计的角度深刻理解CPU硬件结构和指令系统之间的内在联系,了解CPU的设计方法。在综合运用所学知识完成实验的过程中,提升动手能力、科学探究能力,培养精益求精的工匠精神和科技创新意识,树立科技强国的使命担当,成为国家在软件、芯片、高性能计算等领域的储备人才。

本实验遵循计算类专业的培养要求,是独立实验课程《逻辑与CPU设计实验》最后的综合实验环节,也可作为《计算机组成原理》、《计算机硬件基础》等课程的课程设计项目;低起点、高落点、循序渐近的实验设计,使得该实验也适用于对CPU感兴趣的社会学习者。

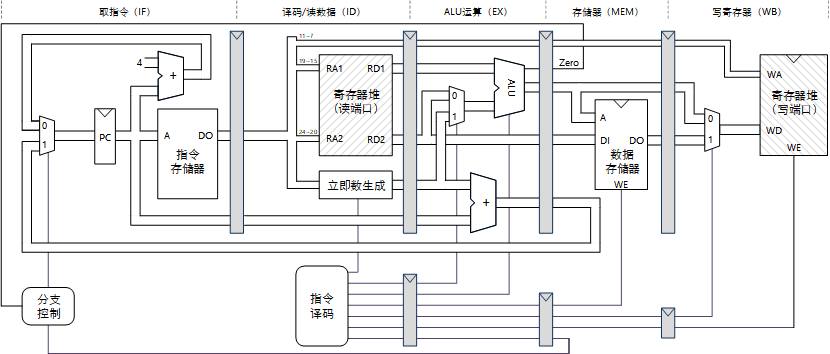

CPU是计算机的核心部件,基本功能是周而复始的执行指令。其内部的控制器根据指令编码产生数据通路所需的控制信号,控制各组成部件有条不紊地运作,从而实现指令的功能。本实验首先设计可执行5条(种)指令的单周期RISC-V CPU,其微结构如图1所示;之后可继续扩充更多的指令,以及设计实现流水线的RISC-V。

图1 支持5条(种)指令的单周期RISC-V CPU 的微结构

为解决芯片内部CPU运行状况无法观察等传统实验技术面临的困境,江苏大学计算机学院教学团队自主研发虚拟实验和远程实验技术,2018年上线了远程FPGA虚拟实验平台,获得了2项国家发明专利授权和3项软件著作权。实验平台将真实的硬件实验板置于云端,学习者通过浏览器中的虚拟界面操作网络另一端实验室中的硬件设备,实现硬件实验的虚实深度交互,突破硬件实验地域限制。虚拟实验平台将云端实验CPU工作过程中产生的真实实验数据,通过可视化技术实时、形象地呈现在用户端,虚实结合,以虚补实,解决了传统实验方式CPU调试过程抽象、运行过程难以观察的局限。实验过程可记录和回放,实现实验任务自动测试评分,解决了远程实验方式下教师检查和反馈的难题。

CPU设计包括指令系统设计、数据通路和控制器设计。

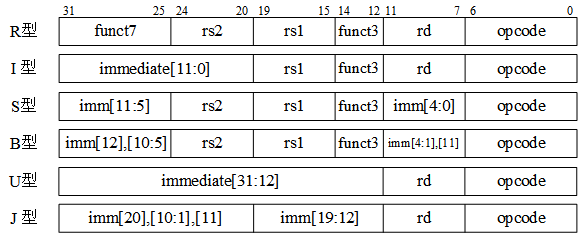

指令系统是软件与硬件的接口。本实验采用最新的开放RISC-V指令集架构,它具有简单规整、模块化可扩展等优点,2014年免费开放后已经有很多企业投入RISC-V芯片的设计和制造,有望成为芯片行业的Linux。RISC-V的几种指令格式如图2所示。

图2 RISC-V指令格式

本实验实现其中部分整数运算指令、访存指令和分支指令。整数运算指令采用R型或者I型指令格式,由opcode字段指定运算类型,指令完成的功能是rd<-(rs1)op(rs2)或者rd<-(rs1)op imm。访存指令包括Load指令和Store指令,其中Load指令采用I型指令格式,功能是将存储器中以[(rs1)+imm]为地址的存储单元内容装入rd寄存器,即rd<-[(rs1)+imm];Store指令采用S型指令格式,功能将rs2寄存器内容保存到以[(rs1)+imm]为地址的存储单元中,即(rs2)->[(rs1)+imm]。分支转移指令采用B型格式,根据条件是否满足决定目标指令的地址,条件成立时用imm与PC值之和作为目标地址,否则用PC值加4作为目标地址。

数据通路的设计是实现指令功能的重要一步。不同的指令,实现它们的数据通路不同;即使是相同的指令,也可能有不同的数据通路设计。本实验通过逐条增加指令的方法,一步步扩充数据通路,从而深刻理解数据通路与指令系统的内在联系。具体在后面的实验内容及步骤中体现。

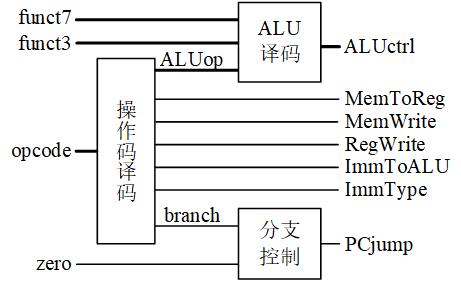

控制器根据指令产生数据通路的各种控制信息,如图3所示。

图3 控制器框图

opcode决定了指令类型,根据它产生数据通路上的大部分控制信号;ALU的运算功能还跟funct3和funct7有关;而分支指令是否转移取决于运算结果是否为零。RISC-V属于精简指令集架构,非常有利于控制器的设计,仅需简单的译码逻辑即可实现。

CPU设计是一个相对复杂的过程,将所有指令和功能一次性全部实现有一定难度。本实验先从支持一条指令的RISC-V CPU入手,再不断扩充处理器的指令。在完成单周期RISC-V CPU的基础上,进一步设计实现5级流水线的RISC-V CPU。

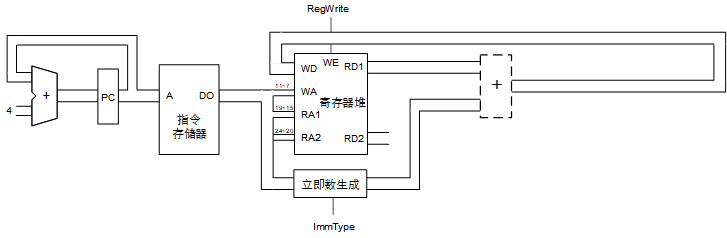

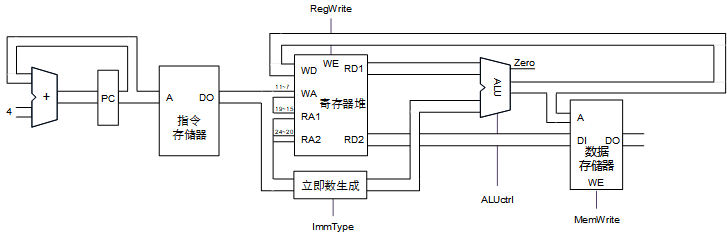

首先通过对只支持一条addi指令的RISC-V CPU(数据通路如图4)的验证分析 ,理解数据通路,熟悉操作环境,掌握验证调试分析方法。

图4 只支持addi指令的RISC-V CPU通路图

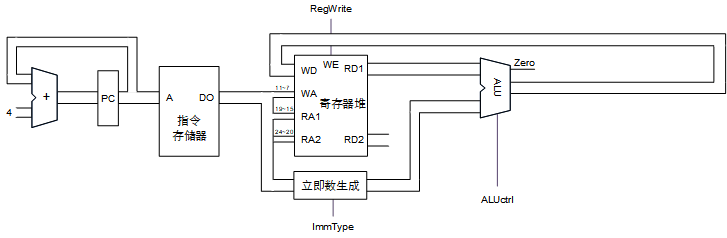

设计支持其他Ⅰ型运算指令,数据通路如图5。在上一步数据通路的基础上,设计ALU模块,用ALU模块替换加法器;修改参考设计的控制器模块,增加ALU控制信号;修改数据通路,连接ALU和控制器。

图5 支持Ⅰ型运算指令的RISC-V数据通路图

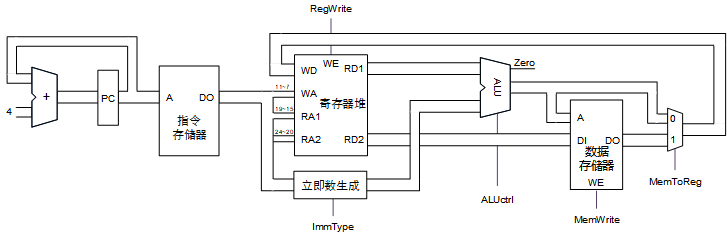

设计支持store类指令,数据通路如图6。在上一步数据通路的基础上,设计数据存储器添加到数据通路;增加S型立即数的生成;修改控制器的设计使其支持sw指令。

图6 支持store指令的数据通路图

设计支持load类指令,数据通路如图7所示。在上一步数据通路的基础上,在数据存储器的输出端设计添加一个多路器,从ALU的输出端和数据存储器的输出端选择写入寄存器堆的数据。

图7 支持load指令的数据通路图

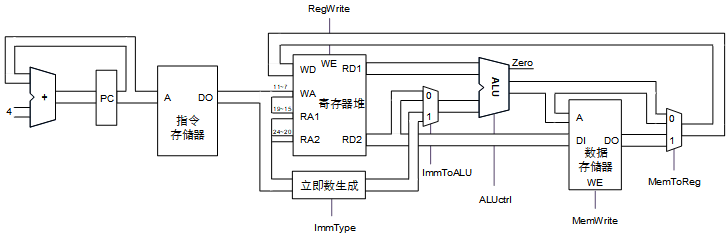

设计支持R型运算指令,数据通路如图8所示。在上一步数据通路的基础上,在ALU的输入端添加一个多路器,用来选择参加运算的一个操作数是来自立即数还是来自寄存器堆。

图8 支持R型运算指令的数据通路

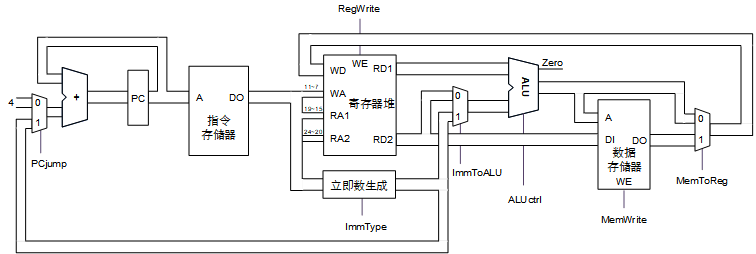

设计支持beq分支指令,数据通路如图9所示。在上一步数据通路的基础上,修改数据通路和控制器的设计,增加B型立即数的生成,增加一个多路器,用于选择PC是加4还是加相对转移地址。

图9 支持分支指令的数据通路

设计支持更多指令的单周期RISC-V CPU并调试,实现更多的 RISC-V 指令,例如lui、auipc、jal等指令。通过逐步增加指令及其对应的数据通路完成更完整的CPU的设计。

设计支持指令流水线,数据通路如图10。RISC-V流水线数据通路的设计是在单周期数据通路的基础上,通过4个流水线寄存器分割指令执行的5个阶段。在指令重叠执行过程中数据通路中同时有5条指令在执行,提高了指令执行的吞吐量。

图10 RISC-V CPU的5级流水线数据通路